# HPI Future SOC Lab - Proceedings 2011

Christoph Meinel, Andreas Polze, Gerhard Oswald, Rolf Strotmann, Ulrich Seibold, Doc D'Errico (Hrsg.)

#### Technische Berichte Nr. 70

des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.de/ abrufbar.

#### **Universitätsverlag Potsdam 2013**

http://verlag.ub.uni-potsdam.de/

Am Neuen Palais 10, 14469 Potsdam Tel.: +49 (0)331 977 2533 / Fax: 2292 E-Mail: verlag@uni-potsdam.de

Die Schriftenreihe **Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam** wird herausgegeben von den Professoren des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam.

ISSN (print) 1613-5652 ISSN (online) 2191-1665

Das Manuskript ist urheberrechtlich geschützt.

Online veröffentlicht auf dem Publikationsserver der Universität Potsdam URL http://pub.ub.uni-potsdam.de/volltexte/2013/6400/URN urn:nbn:de:kobv:517-opus-64004 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-64004

Zugleich gedruckt erschienen im Universitätsverlag Potsdam: ISBN 978-3-86956-230-8

# **Contents**

| Spring 2011                                                                                                  |

|--------------------------------------------------------------------------------------------------------------|

| Prof. Dr. Ben Juurlink, Architektur eingebetteter Systeme, Technische Universität Berlin                     |

| A Benchmark Suite for Evaluating Parallel Programming Models                                                 |

| Prof. Dr. Christoph Meinel, Internet-Technologies and Systems Group, Hasso-Plattner-Institut                 |

| Towards Multi-Core and In-Memory for IDS Alert Correlation: Approaches and Capabilities . 7                  |

| Elastic VM for Dynamic Virtualized Resources Provisioning and Optimization                                   |

| VMs Core-allocation scheduling Policy for Energy and Performance Management                                  |

| Prof. Dr. Holger Giese, System Analysis and Modeling Group, Hasso-Plattner-Institut                          |

| Towards Scalable and Self-Optimizing Software for Multi-Core and Cloud Computing II 25                       |

| Dr. Martin von Löwis, Operating Systems & Middleware Group, Hasso-Plattner-<br>Institut                      |

| Buildbot Project Progress Report                                                                             |

| Prof. Dr. Andreas Polze, Operating Systems & Middleware Group, Hasso-Plattner-Institut                       |

| Downtime Analysis for Pro-Active Virtual Machine Migration Report for the HPI Future SOC Lab                 |

| Prof. Dr. Rainer Thome, Business Administration and Business Information Integration, University of Würzburg |

| Forward Business Recommendations – Realtime Management Support based on In-Memory Technology                 |

| Fall 2011                                                                                                    |

| Prof. Dr. Christoph Meinel, Internet-Technologies and Systems Group, Hasso-Plattner-Institut                 |

| Accurate Mutlicore Processor Power Models for Power-Aware Resource Management 45                             |

| Towards Multi-Core and In-Memory for IDS Alert Correlation: Approaches and Capabilities . 53                 |

| Prof. Dr. Felix Naumann, Information Systems, Hasso-Plattner-Institut                                        |

| Duplicate Detection on GPUs                                                                                  |

| Prof. Dr. Michael Schöttner, Betriebssysteme, Universität Düsseldorf                                    |    |

|---------------------------------------------------------------------------------------------------------|----|

| ECRAM (Elastic Cooperative RAM) HPI Future SOC Lab Project Report                                       | 63 |

| Prof. Dr. h.c. Hasso Plattner, Enterprise Platform and Integration Concepts,<br>Hasso-Plattner-Institut |    |

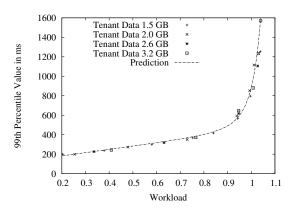

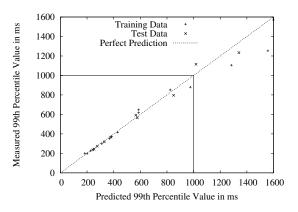

| Performance Prediction for Main Memory Databases in Data Clouds                                         | 67 |

| Prof. Dr. Andreas Polze, Operating Systems & Middleware Group, Hasso-Plattner-Institut                  |    |

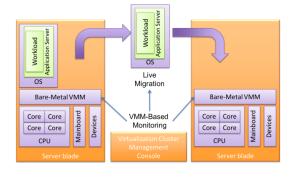

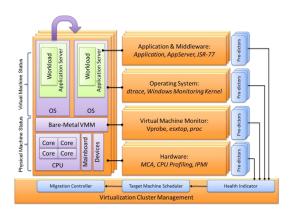

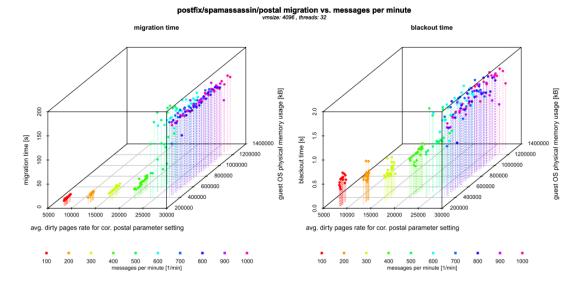

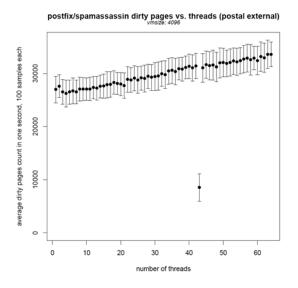

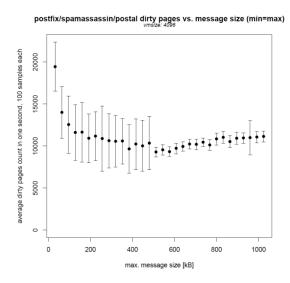

| Downtime Analysis for Pro-Active Virtual Machine Migration                                              | 73 |

#### A Benchmark Suite for Evaluating Parallel Programming Models

Michael Andersch, Ben Juurlink, and Chi Ching Chi Technische Universität Berlin Einsteinufer 17 10587 Berlin {andersch,juurlink,cchi}@cs.tu-berlin.de

#### **Abstract**

The transition to multi-core processors enforces software developers to explicitly exploit thread-level parallelism to increase performance. The associated programmability problem has led to the introduction of a plethora of parallel programming models that aim at simplifying software development by raising the abstraction level. Since industry has not settled for a single model, however, multiple significantly different approaches exist. This work presents a benchmark suite which can be used to classify and compare such parallel programming models and, therefore, aids in selecting the appropriate programming model for a given task. After a detailed explanation of the suites design, preliminary results for two programming models, Pthreads and OmpSs/SMPSs, are presented and analyzed, leading to an outline of further extensions of the suite.

#### 1. Introduction

The move towards multi-core architectures changes the programmers view of the architecture and introduces yet unresolved programmability issues. Increasing performance now requires the explicit exploitation of thread-level parallelism. The development of parallel programs is generally not a trivial task since an appropriate parallel decomposition of the algorithms needs to be found. Additionally, the programmer usually has to perform architecture-specific optimizations such as thread-to-core mapping and page placement, which could lead to different optimal parallelization strategies for different platforms. Furthermore, the verification and debug processes of such programs introduce additional difficulties caused by the complexity associated with sophisticated threads running in parallel.

All this has led to the introduction of several *programming models* in an attempt to relieve developers partly or completely from such parallel programming issues. These models, however, differ significantly in the pro-

vided underlying parallel principles, abstraction levels, semantics, and syntax.

This work aims at providing some means of comparison by introducing an *evaluation suite* consisting of several applications to examine and classify the features and qualities of shared memory parallel programming models. These applications will not only be used as benchmarks to measure performance levels of programs developed in a particular model, but also to evaluate the usability and features of that model. Additionally, a first version of this suite is presented along with preliminary results for two currently relevant models. The contributions of this work can be summarized as follows:

- We propose a benchmark suite specifically targeted at the evaluation of performance and usability of parallel programming models rather than parallel machines.

- We focus on modularity and portability for the benchmarks incorporated into the suite.

- We perform a case study, evaluating the novel OmpSs programming model [10], using POSIX threads as a reference for comparison.

This paper is structured as follows. Section 2 encompasses the top-level design decisions made in creating the evaluation suite. In Section 2.1, we define general requirements the suite must fulfill. In Section 2.2, these requirements are utilized to create a preliminary selection of benchmarks which are then presented in a more detailed fashion. A case study using the benchmark suite is presented and analyzed in Section 3. Section 4 discusses related work. Finally, in Section 5, conclusions are drawn and future perspectives are given.

#### 2. Suite Design

On a high level, the benchmark suite must fulfill several critical requirements which can be derived from its objective as a suite to evaluate the programmability and performance of parallel programming models.

These criteria will then function as guidelines for the selection of benchmarks and benchmarking practice. In the following section, we identify six such criteria. They assure comparability, fairness and ease of use as well as enabling developers using the suite to gather hands-on experience with the programming model in use. Please read the following carefully.

#### 2.1. General Requirements

- 1. A broad range of application domains must be covered.

- 2. Various parallel patterns and characteristics must be covered.

- 3. Various application sizes must be covered.

- The suite must include input data sets of varying size.

- 5. Simplicity, modularity and portability must be ensured.

- The parallelization approach must be fixed and well documented.

#### 2.2. Benchmark Suite

The current benchmark suite is presented in Table 1. The **K**, **W**, and **A** identifiers in the second column are a realization of the third requirement, grouping benchmarks into one of three different categories, **K**ernels, **W**orkloads, and **A**pplications. A kernel consists of (a part of) the extracted core of a real-world application. Kernels are, therefore, comparably small (< 1000 LOC) and exhibit only a single, isolated parallelization pattern.

Workloads are either derived by combining several kernels, thereby introducing additional data dependencies and covering more parallelization patterns, or it is a program considered too large to fit in the kernel class, but still only an extracted part of a real application.

Applications are full-grown software products which are widely used in industry or science and therefore feature the highest number of subsystems, dependencies and combinations of parallelization patterns.

Following is, in the order depicted in Table 1, a short description of each benchmark. It should be kept in mind this is a preliminary selection which shows the current and not the final state of the suite and is subject to change and extension.

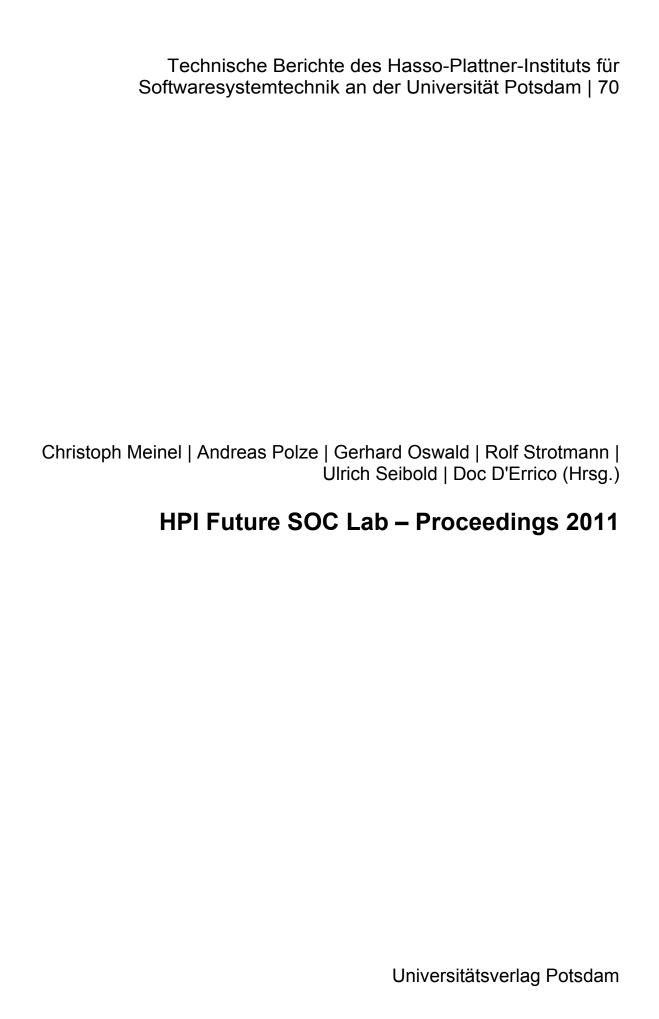

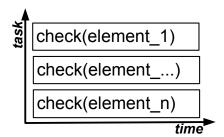

1) c-ray: c-ray is a simple, brute-force ray tracer [17]. It is small (ca. 500 LOC for the serial version) and renders an image in PPM binary format from a simple scene description file. Despite its simplicity, c-ray is a very compute-intensive benchmark, featuring a high computation-to-communication ratio. The parallelization approach is depicted in Figure 1.

Figure 1. Parallel pattern for c-ray, rotate and rgbcmy kernels

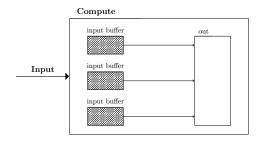

Figure 2. Parallel pattern for md5 kernel

- 2) md5: md5 is a benchmark utilizing a standard implementation of the MD5 hash algorithm [15] to produce hash values. Since there is no exploitable thread-level parallelism in the block cipher construction used in MD5, the benchmark uses multiple input buffers consisting of predefined raw binary data which it processes in parallel. This structure is shown in Figure 2; hatched parts illustrate the exploitable parallelism.

- 3) rgbcmy: The rgbcmy kernel converts an input RGB PPM image to the CMYK color space used for image printing. Parallelism is found in the different pixels (which can be converted independently), visualized in Figure 1.

- *4) rotate: rotate* is a benchmark which rotates an RGB image in binary representation by 0, 90, 180 or 270 degrees. The parallelization approach can also be visualised by Figure 1.

- 5) kmeans: The kmeans kernel executes the k-Means clustering algorithm [8] used in the domains artificial intelligence and data mining. It is derived from the correspondent benchmark in the NU-MineBench benchmark suite [9]. The algorithm is visualized in Figure 3.

Figure 3. Algorithm for kmeans kernel

| Name    | Type | Application        | Domain                  | Problem Sizes       | Code Size |

|---------|------|--------------------|-------------------------|---------------------|-----------|

| c-ray   | K    | Offline Raytracing | Computer Graphics       | 18 / 192 objects    | 500 LOC   |

| md5     | K    | MD5 Calculation    | Cryptography            | various             | 1000 LOC  |

| rgbcmy  | K    | Color Conversion   | Image Processing        | 3.8 / 30.5 MP       | 700 LOC   |

| rotate  | K    | Image Rotation     | Image Processing        | 3.8 / 30.5 MP       | 1000 LOC  |

| kmeans  | K    | k-Means Clustering | Artificial Intelligence | various             | 600 LOC   |

| rot-cc  | W    | rotate + rgbcmy    | Combined Workload       | 3.8 MP / 30.5 MP    | 1400 LOC  |

| ray-rot | W    | c-ray + rotate     | Combined Workload       | 18 / 192 objects    | 1300 LOC  |

| h264dec | A    | H.264 Decoding     | Video Processing        | Full HD / QHD video | 20000 LOC |

Table 1. Benchmarks

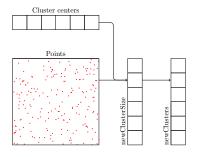

6) rot-cc: As mentioned before, workloads consist of combinations of kernels. The first workload combines the rotate and rgbcmy kernels and is therefore called rot-cc (for rotation + color conversion). The parallelization structure is illustrated in Figure 4. Interesting cases are those where the rotation changes the image orientation (90 and 270 degrees) since this leads to a strided memory access pattern for the color conversion kernel.

Figure 4. Parallel patterns for rot-cc workload

7) ray-rot: By chaining the *c-ray* and rotate kernels, we obtain the *ray-rot* workload. It exhibits additional functionlevel parallelism and is especially interesting because the two phases are highly different in characteristics and must, therefore, be load balanced to achieve high performance. *ray-rot* can be visualized as two chained stages of the pattern in Figure 1.

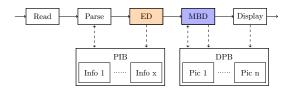

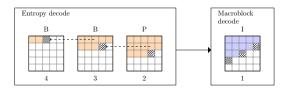

8) h264dec: h264dec is an H.264 decoder [5], derived from FFmpeg, a free, universal video transcoder [6]

For the H.264 decoder benchmark, parallelism is exploited at two levels: function-level and data-level parallelism (DLP). First, in the decoder stages, each stage can be performed in parallel in a pipeline fashion on different frames as shown in Figure 5. Additionally, DLP is exploited within the entropy (ED) and macroblock decoding (MBD) stages. This is illustrated in Figure 6. Here, hatched blocks denote data that can be processed in parallel.

#### 3. Case Study: Pthreads vs. OmpSs

We now present performance results and the documentation of usage experiences comparing two programming models, Pthreads and OmpSs/SMPSs [10].

Figure 5. Pipeline parallelism in h264dec

Figure 6. DLP parallelism in ED and MD stages

In Section 3.1, we describe the features of the programming models in comparison. After the experimental setup is presented in Section 3.2, Section 3.3 compares the speedup characteristics of the different benchmarks. From this comparison, we then derive information about the benchmark behavior and gain a first impression on how the two models compare to each other.

#### 3.1. Evaluated Programming Models

The POSIX thread library [7] provides basic threading support for the C programming language. Synchronization is achieved using mutexes to protect critical sections and condition variables to achieve thread synchronization. The threads themselves have to be created, managed (i.e., set to a certain priority or in a detached state) and terminated explicitly. Pthreads thus fully leaves the management of the parallel algorithm to the programmer, enforcing him or her to consider dependencies, synchronization points, and possible race conditions in a direct, exposed way.

OmpSs/SMPSs [10] is the SMP instance of the OpenMP SuperScalar model (OmpSs). It is a novel task-based programming model which consists of

a runtime library and a source-to-source compiler. SMPSs requires the programmer to annotate functions as tasks using #pragma css task directives and label every task argument as an input, output, inout, or reduction parameter. These keywords declare an argument either read-only, write-only, read-write or as part of a reduction operation. Once such a task is created, it will be added to a runtime data structure, called the task dependency graph. The task graph is maintained and populated by the underlying runtime system which performs the dependency resolution and the scheduling of tasks on worker threads. This is similar to the way a superscalar processor dispatches instructions to available execution units. The only additional synchronization constructs SMPSs provides to the programmer are a barrier directive, which requires all previously created tasks to finish, a wait on directive, used to wait for a certain task to complete, and a mutex, which currently is required for reduction operations. An advantage of SMPSs is that the serial base code is maintained, allowing profiling and debugging of the sequential code with established tools. Its functionality can easily be regained by compiling an SMPSs program with a compiler not recognizing the preprocessor pragmas.

#### 3.2. Experimental Setup

All available results have been obtained during the development of this benchmark suite and are therefore neither specifically optimized nor have been analyzed in detail. Their main objective at this stage is to classify and analyze the early benchmark behavior. Due to this early state of the described benchmarks, results for kmeans and h264dec are not yet included. Our evaluation platform is a 64-core cc-NUMA system with the following features:

- 8x Xeon X7560 (Nehalem EX architecture),

- 2.26 GHz clock frequency,

- HyperThreading disabled,

- 2 TB RAM,

- 204.8 GB/s aggregate memory bandwidth.

Each reported result is the average of three runs. Timing is done using timestamps inside the benchmarks and always excludes the I/O-phases (i.e., loading the input from disk into memory and cleaning up). Additionally, the execution time of all programs has been measured using both a small and a large input data set (see Table 1 for details).

#### 3.3. Preliminary Scaling Results

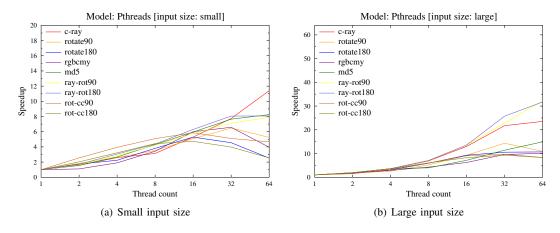

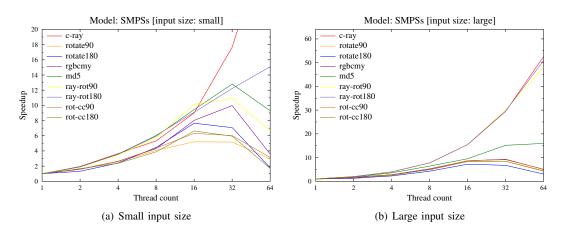

In this section, the preliminary results for the Pthreads and SMPSs versions of the benchmarks are discussed.

The speedup has been obtained by dividing the execution time on one processor by the execution time on n processors for the same program, thus normalizing the speedup factor for a single core to one.

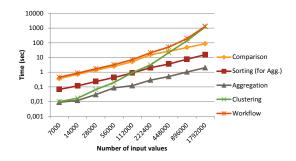

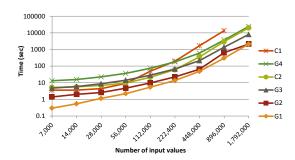

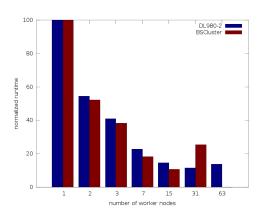

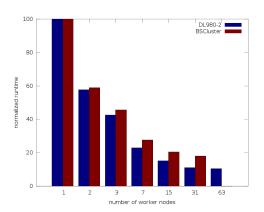

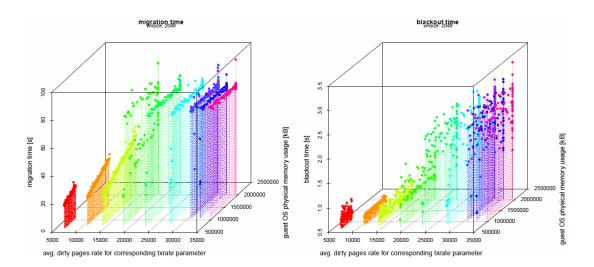

The speedup results for up to 64 cores for the Pthreads programming model using small input data sets are shown in Figure 7(a), the ones for large input data in Figure 7(b). The corresponding ones for SMPSs can be found in Figures 8(a) and 8(b).

The figures show that the behavior varies widely across the applications. For the highest thread count of 64, the Pthreads benchmarks achieve speedup factors ranging from 2.53x to 11.4x for the small and from 10.1x to 31.7x for the large input data sets. For the same number of threads, the SMPSs benchmarks achieve speedups between 1.7x and 33.4x for the small and 3.0x and 52.5x for the large input data sets. The differences observed between small and large input sizes are caused by the naturally higher amounts of DLP, leading to a coarsened granularity of the work units and thus diminishing the impact of the threading overhead. The results show that regarding only speedup and not real execution time, for these benchmarks, SMPSs performs on average two times better than Pthreads. For SMPSs, the runtime must be initialized before and shut down after any calls to it are made. This is excluded from the timing, while for Pthreads, thread creation is mostly tightly coupled with the actual execution and is therefore generally included. This is one of the reasons for the higher speedups of SMPSs.

The highest speedups are achieved for benchmarks which include ray tracing. This is expected since c-ray has a high computation-to-communication ratio. The performance of the Pthreads version of the c-ray kernel for large inputs saturates, however. In this case, performance increases by only 8% when going from 32 to 64 threads, compared to an average 70% for the other test cases (Figures 7(a), 8(a), 8(b)). This is fully reproducable and will be investigated further.

The lowest speedups are achieved by benchmarks which include the rotate kernel (and do not also include ray tracing). The reason for this supposedly is the cc-NUMA evaluation platform. Because there is only a small amount of computation in the rotate kernel, increasing the thread count does not improve performance but instead leads to memory contention, causing a high amount of (coherence) traffic. This is especially the case for the transition from 32 to 64 threads where four additional processor sockets are used for 64 threads, resulting in a lower speedup than for 32 threads.

A deeper analysis of these observations and further machine-specific optimizations are future work.

Figure 7. Baseline performance for Pthreads

Figure 8. Baseline performance for OmpSs/SMPSs

#### 4. Related Work

Benchmark suites have been developed previously, including several proprietary, domain-specific products [2, 16]. They are, however, mainly non-compliant with the portability concept our work chooses to follow.

PARSEC [3, 4] is a recent benchmark suite consisting of 12 programs. The target platforms of PARSEC originally are chip multiprocessors, however, the programs included in the suite are not inherently limited to this usage scenario. The stated goal of PARSEC is to discover new trends in the research and development of parallel machines, algorithms and applications. Featured for all benchmarks are variants for Pthreads, OpenMP and Intel Thread Building Blocks. However, PARSECs set goal is also to provide a fix framework for benchmark execution, input data size control and installation. This complicates the processes of extending the suite quickly or extracting an application out of it for further, isolated use.

Apart from benchmark suites, previous work also includes attempts particularly targeted at the evaluation of parallel programming models.

Podobas et al. [11] performed an evaluation of three

taskbased parallel programming models, OpenMP, Cilk++ and Wool. They focus on leveraging the performance characteristics of these parallel programming models, studying in detail the cost of creating, spawning and joining tasks as well as overall performance. The results are limited to only three programming models, only kernel-type programs and only performance characteristics. Moreover, the work excludes the extension to new programming models and therefore is, in contrast to our work, not portable.

Ravela [14] presents an evaluation of Intel TBB, Pthreads, OpenMP and Cilk++, containing results for both achieved performance and the time required to develop the respective versions of the benchmarks. All used benchmarks are, however, taken from the domain of high performance computing, resulting in limited relevance for different application domains.

#### 5. Conclusions and Future Work

In this paper, we presented a benchmark suite to evaluate the programmability and performance of emerging parallel programming models. To achieve this, we focused on a structured, portability-focused, fixed-

parallelism approach. We analyzed the intended usage of the suite, thereby compiling a set of requirements which must be met by a benchmark suite aimed at evaluating parallel programming models. We presented and described an early collection of such benchmarks, covering a wide range of application domains, and used them in case study, comparing an established with an emerging programming model.

The preliminary experimental results obtained in this process have shown a wide range of characteristics for the chosen benchmark set, especially giving insights about the behavioral properties of those benchmarks and producing valuable information on the scaling and speedup characteristics of the two analyzed programming models. This study must also be extended to additional types of parallel machines, for example heterogeneous architectures or large chip multiprocessors. Such an investigation could also include a detailed analysis of the statistical features of each benchmark, resulting in concrete measures for properties such as bandwidth usage, arithmetic complexity or memory size requirements.

Naturally, our benchmark suite will be subject to extension. As mentioned in Section IV, porting suitable, existing opensource benchmarks from other collections to this suite is ongoing work. Furthermore, we seek to extend the suite with additional, industryrelevant applications in order to gain key insights on how modern programming models fare when used in large, real-world applications. Benchmarks currently being considered are POV-Ray [1] or a game engine. Aside from adding more benchmarks to the suite, another goal is to evaluate more programming models to gather more experiences in using the suite. Evaluating a larger number of programming models is naturally an advantage because it will provide more references to compare to when evaluating new programming models.

#### Acknowledgment

This research has been supported in part by the European Communitys Seventh Framework Programme [FP7/2007-2013] under the ENCORE Project (www.encore-project.eu), grant agreement no 248647 [13], and the Future SOC Lab of Hasso-Plattner-Institute Potsdam [12].

#### References

- [1] Persistence of vision ray tracer. http://www.povray.org/, 2011.

- [2] M. Berry. Public international benchmarks for parallel computers: Parkbench committee: Report-1. Technical report, Scientific Program, 1994.

- [3] C. Bienia. *Benchmarking Modern Multiprocessors*. PhD thesis, Princeton University, 2011.

- [4] C. Bienia and K. Li. PARSEC 2.0: A New Benchmark Suite for Chip-Multiprocessors. In *Proceedings of the 5th Annual Workshop on Modeling, Benchmarking and Simulation*, 2009.

- [5] C. C. Chi and B. Juurlink. A QHD-Capable Parallel H.264 Decoder. In *Proceedings of the 25th International Conference on Supercomputing*, 2011.

- [6] FFmpeg group. http://www.ffmpeg.org/ffmpeg.html, 2011.

- [7] IEEE Opengroup. Portable Operating System Interface. 2004.

- [8] J. B. MacQueen. Some methods for classification and analysis of multivariate observations. In *Proceedings of the Fifth Berkeley Symposium on Mathematical Statistics and Probability*, 1967.

- [9] R. Narayanan, B. Özisikyilmaz, J. Zambreno, G. Memik, and A. Choudhar. Minebench: A benchmark suite for data mining workloads. In *Proceedings* of the International Symposium on Workload Characterization (IISWC), 2006.

- [10] J. Perez, R. Badia, and J. Labarta. A Dependency-Aware Task-Based Programming Environment for Multi-Core Architectures. In *IEEE International Con*ference on Cluster Computing, 2008.

- [11] A. Podobas, M. Brorsson, and K.-F. Faxén. A comparison of some recent task-based parallel programming models. In *Third Workshop on Programmability Issues for Multi-Core Computers*, 2010.

- [12] H.-P.-I. Potsdam. Future soc lab. http://www.hpi.uni-potsdam.de/forschung/future soc lab.htm, 2011.

- [13] E. Project. Enabling technologies for a future manycore., 2011.

- [14] S. C. Ravela. Comparison of shared memory based parallel programming models. Master's thesis, Biekinge Institute of Technology, 2010.

- [15] R. Rivest. The MD5 Message-Digest Algorithm. 1992.

- [16] Standard Performance Evaluation Corporation. SPEC Benchmark Suite. http://www.spec.org/index.html, 2011.

- [17] J. Tsiombikas. http://www.futuretech.blinkenlights.nl/c-ray.html, 2010.

#### Towards Multi-Core and In-Memory for IDS Alert Correlation: Approaches and Capabilities

Sebastian Roschke Hasso-Plattner-Institute Prof.-Dr.-Helmert-Str. 2-3 14482 Potsdam sebastian.roschke@hpi.uni-potsdam.de Feng Cheng Hasso-Plattner-Institute Prof.-Dr.-Helmert-Str. 2-3 14482 Potsdam feng.cheng@hpi.uni-potsdam.de

Christoph Meinel Hasso-Plattner-Institute Prof.-Dr.-Helmert-Str. 2-3 14482 Potsdam meinel@hpi.uni-potsdam.de

#### **Abstract**

Intrusion Detection Systems (IDS) have been widely deployed in practice for detecting malicious behavior on network communication and hosts. The problem of false-positive alerts is usually addressed by correlation and clustering of alerts. As real-time analysis is crucial for security operators, this process needs to be finished as fast as possible, which is a challenging task as the amount of alerts produced in large scale deployments of distributed IDS is significantly high. We identify the data storage and processing algorithms to be the most important factors influencing the performance of clustering and correlation. We implement memory-optimized algorithms and columnoriented or In-memory databases for correlation and clustering in an extensible IDS correlation platform, which leads to significant improvements of the performance. The platform supports multi-core frameworks, such as OpenCL and MapReduce. The efficiency of the proposed platform is tested by practical experiments with several alert storage approaches and different simple algorithms.

#### 1 Alert Correlation and its Performance

The alert correlation framework usually consists of several components [4]: Normalization, Aggregation (Clustering), Correlation, False Alert Reduction, Attack Strategy Analysis, and Prioritization. Over the last years, alert correlation research focused on new methods and technologies for these components. ID-MEF [5] and CVE [6] are important efforts in the field of Normalization. Approaches of aggregation are mostly based on similarity of alerts or generalization

hierarchies. The correlation algorithms [4] can be classified as: *Scenario-based correlation*, *Rule-based correlation*, *Statistical correlation*, and *Temporal correlation*. Most of the efforts do not consider the aspect of performance, which is needed in case of huge amounts of alerts, as well as the scenarios requiring real-time.

The efficiency of the correlation depends on the quality and performance of the algorithm as well as the storage and organization of original alerts. The quality is a measure of the correctness of the algorithm and depicts how many of the recognized correlations are correct, i.e., how many of the correlations found represent existing relations between alerts. Furthermore, it depicts how many of the existing relations between alerts are found by the algorithm. The performance of the correlation describes the amount of time needed to correlate a number of alerts. Due to the complexity of large scale networks, the amount of alerts increases significantly. Therefore, the performance of correlation algorithms is a major aspect of the efficiency of correlation.

The work described in [27] considers the performance of alert correlation by using a memory-based index for hyper alerts. A hyper alert is a cluster of alerts with the same properties, e.g., the same source address or target address. The approach using index tables is introduced in [11]. To perform correlation in real-time, the approach filters and clusters alerts to hyper alerts, which reduces the number of processed alerts significantly. However, this technique may lead to inaccurate results of the correlation, as multiple alerts are generalized to a single hyper alert. The approach reaches a correlation rate on the order of 100,000 alerts per second based on the massive reduction of alerts by clustering in hyper alerts. In [2] the *data storage* and the *processing algorithms* have been identified to be the

most important factors influencing the performance of clustering and correlation. The platform introduced in [2] considers different storage mechanisms and can handle up to 100,000,000 for specific algorithms that make heavy use of the caching mechanisms of the platform. For storage, a column-based database, an In-Memory alert storage, and memory-based index tables lead to significant improvements of the performance. Although this work considers data and task distribution in general, the platform is not mature enough to distribute one correlation algorithm over multiple computing cores. Furthermore, using a hybrid memory architecture and GPU based computing is not considered.

We believe that research in the area of IDS and network security as application for multi-core and Inmemory based platforms can provide new paradigms for conducting security. Correlation and clustering is currently only done in a limited way using filtered data sets. Using the multi-core and In-memory platforms, it might be possible to do correlation and clustering on an unfiltered data set. Thus, it might not be necessary to fine tune (e.g., exclude certain detection rules) the IDS sensors anymore, as the correlation and clustering can do meaningful reasoning on all alerts in a short time. Furthermore, we expect correlation and clustering services offered in the Cloud. A flexible and extensible correlation platform can provide the foundation work for a new paradigm in security.

#### 2. Results and Achievements

During the last few month, we have been able to achieve multiple results by using the system in the Future SOC infrastructure. The existing IDS correlation platform was extended for multi-core processing. We conducted preliminary practical experiments using the existing platform with known algorithms. Apart from the practical achievements, we have been able to publish papers on the correlation platform [2] and started research on a complex correlation algorithm using attack graph data and environmental information for IDS correlation [1]. Some results are summarized in the following subsections.

We deployed the prototype of the correlation platform a FutureSOC VM (1 CPU, 4 GB Ram) and developed multiple features to improve performance and usability. Furthermore, we conducted some tests and experiments using the NVIDIA FluiDyna System. The following feature set has been realized:

- Snort alert generator that generates IDS alerts using a network description

- Dynamic module loading by uploading a module through the frontend

- Usability and performance improvements for the GUI

- Integration of environmental data into the platform that can be used for correlation (network and system descriptions, attack graph data)

- Development of the information pool concept that enables access to correlation results and environmental information for all correlation modules

- Multi-core support for OpenCL and MapReduce

- Visualization of correlation results

# 2.1 Parallel Processing in IDS Correlation

Parallel processing is useful in all steps of the correlation. In most of the steps, the possibility to parallelize the computing depends on the algorithm used to perform this step. The preferred technology for implementing the steps of the correlation highly depends on the chosen algorithm. While algorithms that can be expressed in the MapReduce model can use a data parallel or task-parallel approach and are easier to implement, the OpenCL implemented algorithms are dataparallel and support GPU processing which might be more efficient for specific tasks. A correlation platform needs to support multiple ways for multi-core processing to be useful for most of the algorithms in the correlation framework.

The normalization is data-parallel, as each event can be processed independently. Let  $\mathcal{A}$  be the set of IDS alerts in IDMEF format. Let  $\mathcal{C}$  be the set of events in CEE [7] format. The function  $n: \mathcal{A} \to \mathcal{C}$  is a mapping from  $\mathcal{A}$  to  $\mathcal{C}$  and needs only one parameter as input.

$$n(a_i) = c_i | a_i \in \mathcal{A} \land c_i \in \mathcal{C} \tag{1}$$

Let  $C \subset \mathcal{C}$  be the set of events that is supposed to be aggregated. Let  $\Upsilon_k(x,y)$  be an expression with  $x \in \mathcal{C}, y \in \mathcal{C}$  that represents the aggregation condition. The relation  $R_C$  is defined as:

$$R_C = \{(x, y) \in C^2 : \Upsilon_k(x, y)\}$$

(2)

$R_C^*$  defines an equivalence relation on the transitive closure of  $R_C$ . The alert aggregation combines alerts that are similar and being created together in a short time, i.e., the difference of the timestamps is below a certain threshold. It defines a set of equivalence classes  $C_{/R_C^*}$  over the equivalence relation  $R_C^*$ . As the aggregation needs to be expressed as an relation between two events, the processing needs to be on specific sets of events. Thus, parallelizing the process needs additional efforts and might not be possible for each  $\omega_k(x,y)$ . For instance, if the aggregation condition is true for events with the same message, a classical data-parallel approach could be used. If the aggregation condition is true for events with the same message and with a small difference in timestamps, a data-parallel based approach might not be easy to implement. A fragmentation of the original data set in chunks with events that happened in the same time interval might be a better solution. A task-parallel approach might be used for aggregating events based on different conditions.

The correlation of events is basically a creation of relations between events and thus is similar to the aggregation in terms of parallelization. For instance, a statistical correlation requires counting of similar events and thus might be handled with a data-parallel approach and merging of the counted results. Correlation algorithms are mostly based on specific machine learning algorithms where each computation result depends on input data and on former computation results, a data-parallel approach might not be feasible or easy to implement. The same holds for False Alert Reduction, Attack Strategy Analysis, as well as Prioritization.

As the different steps of the correlation process might be parallelized in different ways, a correlation platform is required to support parallelization approaches natively. Furthermore, programming paradigms, such as MapReduce, can simplify the implementation of the algorithm. Hardware independent implementations of multi-core support, such as OpenCL, provides a high flexibility in deploying the system in different environments.

#### 2.2 A Correlation Platform for Parallel Processing

It is expected that the proposed IDS correlation platform can support both, batch mode and stream mode, as described in [9]. The batch mode is useful for forensic analysis and operates on a fixed set of alerts. The stream mode is useful for realtime analysis for security operations and monitoring of the current state of the network. Obviously, the multi-core functionality helps for the batch mode, as the fixed data set can be parted in chunks and processed in a data-parallel way. Furthermore, the multi-core support can be useful for the stream mode when task-parallel processing is possible. Different independent correlation algorithms can be executed simultaneously on the same set of incoming alerts. The platform should provide an easy-to-use interface for programming and uploading modules. Moreover, it should be capable of connecting different kinds of sensors as well as other management systems by using a unified format for alerts and messages, i.e., IDMEF [5] or CEE[7].

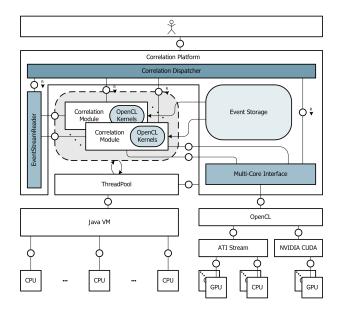

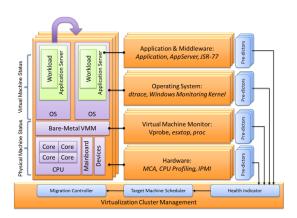

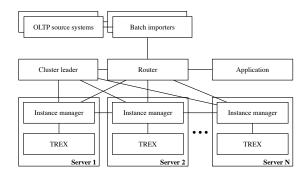

As shown in Figure 1, the platform runs correlation modules as plugins, which improves the extensibility and flexibility of the platform. Each correlation module has the possibility to make use of OpenCL by defining own kernels that are loaded with the module. As soon as the module makes use of OpenCL kernels, it is automatically handled by the OpenCL implementation, either NVIDIA CUDA or ATI Stream. As the ATI Stream API supports both, graphical processing units (GPU) as well as central processing units (CPU),

it is used as the default processing API for OpenCL kernels. Each correlation module runs autonomously as a thread on the Java Virtual Machine (JVM), which is capable of distributing tasks to existing CPUs. The system uses an internal event storage to process events in batch mode. Additionally, the EventStreamReader receives events from IDS sensors and log gatherers at runtime and enables processing in stream mode. The Mutli-Core Interface is responsible for compiling as well as triggering the execution of the OpenCL kernels for each correlation module.

The event storage is an in-memory database that holds all existing events in memory. The number of possible events in the memory depends on the size of the random access memory (RAM) on the hardware the correlation platform is running on. As RAM is getting cheaper and there are systems with up to 2TB of RAM, this approach is now possible. On the running prototype, a basic alert needs about 152 Bytes of allocated memory. The hardware bases of our prototype is a *Hewlett Packard DL980 G7* with 2 TB of main memory, i.e., 2, 199, 023, 255, 552 Bytes. In the ideal situation where we are able to use the full amount of memory for alerts, it is possible to store  $1.44672583*10^{10}$  alerts.

# 3 AG-based Correlation Algorithm using HMM

A more complex correlation algorithm uses attack graphs to correlate alerts. Attack Graphs have been proposed as a formal way to simplify the modeling of complex attacking scenarios. Based on the interconnection of single attack steps, they describe multi-step attacks. Attack Graphs not only describe one possible attack, but many potential ways for an attacker to reach a goal. In an attack graph, each node represents a single attack step in a sequence of steps. Each step may require a number of previous attack steps before it can be executed, denoted by incoming edges, and on the other hand may lead to several possible next steps, denoted by outgoing edges. With the help of attack graphs most of possible ways for an attacker to reach a goal can be computed. This takes the burden from security experts to evaluate hundreds and thousands of possible options. Thus, a program can identify weak spots much faster than a human. At the same time, representing attack graphs visually allows security personal a faster understanding of the problematic pieces of a network [24, 25].

In this paper, we adopted the AG based correlation algorithm as described in [3]. The algorithm consists of three simple steps: 1) the preparation, 2) the mapping, and 3) the building of an alert dependency graph. In the preparation phase, all necessary information is loaded, i.e., the system and network information is gathered, the database with alert classifications is imported, and the attack graph for the network is loaded.

Figure 1. Mutli-Core Platform Architecture

We use a similar mapping function as it is described in [26], i.e., alerts are mapped to match with specific nodes in the attack graph. An alert matches if the alert type matches, e.g., when the alert refers to an existing vulnerability in the network, and the source and target address of the alert fit to the node in the attack graph. To build an alert dependency graph, we are using a Breadth First Search (BFS) on the attack graph and create a dependency between alert  $a_i$  and  $a_i$ , if  $t(a_i) \le t(a_i)$  and  $a_i$  is mapped to a node that can be reached from the node that  $a_i$  is mapped to (t(a)) returns the creation time of the alert a). Each path in the alert dependencies graph identifies a subset of alerts that might be part of an attack scenario. The alert dependency graph can be used for further analysis, e.g., ranking of attack scenarios or manual evaluations of attack scenarios.

To identify the most probable path in the attack graph based on the observed events, a Hidden Markov Model (HMM) is used and the Viterbi path is calculated. By defining an attack graph with its notes as Markov chain of events, the mapping function defines a set of possible observations. The log events are a set of actual observations that can be the input for the Viterbi algorithm that is supposed to find the most probable set of nodes in the HMM that lead to the observations made.

#### 4. Future Work

Within the next few months, we want to prepare the correlation platform for further research and experiments. We would like to work towards our vision with the following steps:

Conduct performance experiments on the improved platform

- Improve multi-core support

- Implement more algorithms with multi-core support

- Research on correlation algorithms that are using environment information and attack graphs

- Research on visualization techniques for correlation results

#### References

- [1] S. Roschke, F. Cheng, Ch. Meinel: *Using Vulnerability Information and Attack Graphs for Intrusion Detection* In: Proceedings of 6th International Conference on Information Assurance and Security (IAS'10), IEEE Press, Atlanta, United States, pp. 104-109 (August 2010).

- [2] Roschke, S., Cheng, F., Meinel, Ch.: An Alert Correlation Platform for Memory-Supported Techniques. In: Concurrency and Computation, Wiley Blackwell, 2011 (to appear).

- [3] Roschke, S., Cheng, F., Meinel, Ch.: A New Correlation Algorithm based on Attack Graph. In: Proceedings of the 4th Conference on Computational Intelligence in Security for Information Systems (CISIS'11), Springer LNCS 6694, Torremolinos, Spain, pp. 58-67 (2011).

- [4] R. Sadoddin, A. Ghorbani: *Alert Correlation Survey: Framework and Techniques*, In: Proceedings of the International Conference on Privacy, Security and Trust (PST'06), ACM Press, Markham, Ontario, Canada, pp. 1-10 (2006).

- [5] Debar, H., Curry, D., Feinstein, B.: The Intrusion Detection Message Exchange Format, Internet Draft, Technical Report, IETF Intrusion Detection Exchange Format Working Group (July 2004).

- [6] Mitre Corporation: Common vulnerabilities and exposures (CVE), WEBSITE: http://cve.mitre.org/ (accessed Apr 2011).

- [7] Mitre Corporation: Common Event Expression (CEE), WEBSITE: http://cee.mitre.org/ (accessed Apr 2011).

- [8] H. Plattner: A Common Database Approach for OLTP and OLAP Using an In-Memory Column Database, In: Proceedings of the ACM SIG-MOD International Conference on Management of Data (SIGMOD'09), ACM Press, Providence, Rhode Island, USA, pp. 1-2 (2009).

- [9] S. Roschke, F. Cheng, Ch. Meinel: An Extensible and Virtualization-Compatible IDS Management Architecture, In: Proceedings of 5th International Conference on Information Assurance and Security (IAS'09), IEEE Press, vol. 2, Xi'an, China, pp. 130-134 (August 2009).

- [10] Tedesco, G. and Aickelin, U.: Real-Time Alert Correlation with Type Graphs, In: Proceedings of the 4th international Conference on Information Systems Security (ISS'09), Springer LNCS 5352, Hyderabad, India, pp. 173-187 (2008).

- [11] Ning, P. and Xu, D.: Adapting Query Optimization Techniques for Efficient Intrusion Alert Correlation, Technical Report, North Carolina State University at Raleigh, 2002.

- [12] Northcutt, S., Novak, J.: *Network Intrusion Detection: An Analyst's Handbook*, New Riders Publishing, Thousand Oaks, CA, USA (2002).

- [13] Breshears, C.: *The Art of Concurrency*, O'Reilly Media, Sebastopol, CA, USA (2009).

- [14] Khronos Group OpenCL, WEBSITE: http://www.khronos.org/opencl/ (accessed Apr 2011).

- [15] Java OpenCL Library (JavaCL), WEB-SITE: http://code.google.com/javacl/ (accessed Apr 2011).

- [16] NVIDIA CUDA, http://www.nvidia.com/object/cuda\_home\_new.html (accessed Apr 2011).

- [17] ATI Stream Technology, WEBSITE: http://www.amd.com/us/products/technologies/stream-technology/Pages/stream-technology.aspx (accessed Apr 2011).

- [18] Dean, J., Ghemawat, S.: *MapReduce: Simplified Data Processing on Large Clusters*, In: Communications of the ACM, ACM Press, 51(1), pp. 107-113 (January 2008).

- [19] Yoo, R.M., Romano, A., Kozyrakis, Ch.: Phoenix Rebirth: Scalable MapReduce on a Large-Scale Shared-Memory System, In: Proceedings of the IEEE International Symposium on Workload Characterization (IISWC'09), IEEE Press, Austin, TX, pp. 198-207 (September 2009).

- [20] Mao, Y., Morris, R., Kaashoek, F.: Optimizing MapReduce for Multicore Architectures, Technical Report MIT-CSAIL-TR-2010-020, MIT, 2010.

- [21] Apache Hadoop Project, WEBSITE: http://hadoop.apache.org/ (accessed Apr 2011).

- [22] Arnes, A., Valeur, F., Vigna, G., Kemmerer, R.: Using Hidden Markov Models to Evaluate the Risks of Intrusions: System Architecture and Model Validation. In: Proceedings of the International Symposium on Recent Advances in Intrusion Detection (RAID'06), Springer LNCS 4219, Hamburg, Germany, pp. 145-164 (2006).

- [23] MacQueen, J.B.: Some Methods for classification and Analysis of Multivariate Observations. In: Proceedings of 5th Berkeley Symposium on Mathematical Statistics and Probability, University of California Press, pp. 281-297 (1967).

- [24] Sheyner, O., Haines, J., Jha, S., Lippmann, R., Wing, J.M.: Automated Generation and Analysis of Attack Graphs. *Proceedings of the 2002 IEEE Symposium on Security and Privacy (S&P'2002)*, IEEE Press, Los Alamitos, CA, pp. 273-284 (2002).

- [25] Noel, S., Jajodia, S.: Managing attack graph complexity through visual hierarchical aggregation. *Proceedings of Workshop on Visualization and Data Mining for Computer Security (VizSEC/DMSEC 2004)*, ACM Press, New York, NY, USA, pp. 109-118 (2004).

- [26] Wang L, Liu A, Jajodia S. Using attack graphs for correlation, hypothesizing, and predicting intrusion alerts. *Computer Communications*, 29(15), pp. 2917-2933 (April 2006).

- [27] Tedesco, G. and Aickelin, U.: Real-Time Alert Correlation with Type Graphs, In: Proceedings of the 4th international Conference on Information Systems Security (ISS'09), Springer LNCS 5352, Hyderabad, India, pp. 173-187 (2008).

# Elastic VM for Dynamic Virtualized Resources Provisioning and Optimization

Christoph Meinel, Wesam Dawoud, and Ibrahim Takouna

Hasso Plattner Institute (HPI)

University of Potsdam

Potsdam, Germany

{christoph.meinel, wesam.dawoud, ibrahim.takouna}@hpi.uni-potsdam.de

#### **Abstract**

Rapid growth of E-Business and frequent changes in websites contents as well as customers interest make it difficult to predict workload surge. To maintain a good quality of service (QoS), system administrators must provision enough resources to cope with workload fluctuations considering that resources overprovisioning reduces business profits while underprovisioning degrades performance. In this project, we present elastic system architecture for dynamic resources management and applications optimization in virtualized environment. In our architecture, we have implemented three controllers: CPU, Memory, and Application. These controllers run in parallel to guarantee efficient resources allocation and optimize application performance of co-hosted Virtual Machines (VMs) dynamically. We evaluated our architecture with extensive experiments and several setups; the results show that considering online optimization of application, with dynamic CPU and Memory allocation, can reduce service level objectives (SLOs) violation and maintain application performance.

#### 1. Introduction

Later advance in virtualization technology software, e.g. Xen [1] and VMware [6], enabled cloud computing environment to deliver agile, scalable, elastic, and low cost infrastructures. However, current implementation of elasticity in "Infrastructure as a Service" cloud model considers VM as a scalability unit. In this project, we developed an automated dynamic resources provisioning architecture to optimized resources provisioning in consolidated virtualized environments (e.g., Cloud computing). Unlike current implementation of elasticity in cloud infrastructure, we replaced the VM (i.e., coarse-grain scalability unit) with fine-grain resources units (i.e. CPU%, Memory in MB). Our Elastic VM is scaled dynamically in-place to cope with workload fluctuations. Further-

more, the hosted application is also tuned after each scaling to maintain predetermined (SLOs). As a use case, we implemented our approach into Xen environment and used Apache web server as an application. Our SLO in this project is to keep the response time of the web requests less than a specified threshold.

The key contributions of this work are as follow: First, we have studied Apache application performance under different configuration and different CPU and Memory allocation values. Second, we have developed a dynamic application optimization controller for Apache application to maintain the desired performance. Third, we built CPU and Memory controllers based on [2]. Fourth, we built elastic system architecture that join CPU, Memory, and application optimization controllers for managing consolidated virtualized environments. Finally, the elastic system architecture has been evaluated with extensive experiments on several synthetic workload and experimental setups. Our results show that elastic system architecture can guarantee the best performance for application in terms of throughput and response time.

#### 2. Elastic VM architecture

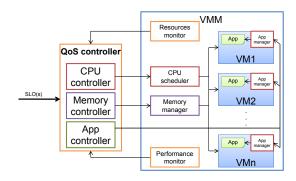

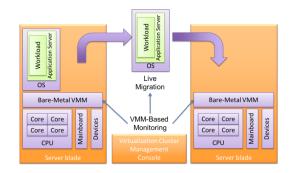

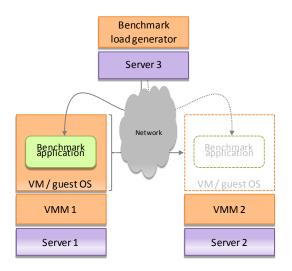

Figure 1. Elastic VM architecture

Our architecture has main component "QoS controller" which communicates with many other mod-

ules implemented into the Virtual Machine Manager (VMM) and VMs levels as the following:

- Resources monitor module dynamically measures the resources consumption and updates the QoS controller with new measurements.

- CPU scheduler is implemented to dynamically change the CPU allocation of the VMs according to determined values by QoS controller, this module depends on Xen credit scheduler as an actuator for setting the CPU shares for VMs.

- Memory manger is implemented with the help of balloon driver in Xen to allows online changing of VMs Memory.

- Performance monitor also keeps the controller up to date with performance metrics, i.e. the average response time and the throughput.

- Application manager (App manager) is implemented into VM level, its job is to get new

MaxClients value from the Application controller

(App controller), to update the Apache configuration file, and then to reload Apache gracefully.

On the left side of figure 1 is the QoS controller; the controller has (SLOs) as inputs and the proposed CPU capacity, proposed Memory allocation, and proposed MaxClients as outputs. In our approach the main SLO is to keep average response time of Apache web server into specific value regardless of the workload fluctuations. For this purpose, we implemented three controllers to run in parallel, these controllers are as the following:

**CPU controller:** Which is a nested loop controller developed in [8]. The inner controller (CPU utilization controller) is an adaptive-gain integral (I) controller was designed in [7]:

$$a_{cpu}(k+1) = a_{cpu}(k) - K_1(k)(u_{cpu}^{ref} - u_{cpu}(k)),$$

(1)

Where

$$K_1(k) = \alpha . c_{cpu}(k) / r_{cpu}^{ref} \tag{2}$$

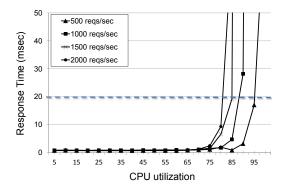

The controller is designed to predict the next CPU allocation  $a_{cpu}(k+1)$  depending on last CPU allocation  $a_{cpu}(k)$  and consumption  $c_{cpu}(k)$ , where the last CPU utilization  $u_{cpu}(k)=c_{cpu}(k)=a_{cpu}(k)$ . The parameter  $\alpha$  is the constant gain that determines the aggressiveness of the controller. In our experiments, we set  $\beta$ =1.5 to allow the controller to aggressively allocate more CPU when the system is overloaded, and slowly decrease CPU allocation at low workload. The disadvantage of this controller is that, it implies determining the reference utilization  $u_{cpu}^{ref}$  manually. However, this is not practical while as seen in figure 2, the response time does not only depend on CPU utilization, but also on the request rate, which changes frequently. So, it is

more realistic to have  $u^{ref}_{cpu}$  value automatically driven by the application's QoS goals rather than being chosen manually for each application. For this goal, another outer loop controller (RT controller) is designed [8] to adjust the  $u^{ref}_{cpu}$  value dynamically. The outer loop controller can be interpreted as the following:

$$u_{cpu}^{ref}(i+1) = u_{cpu}^{ref}(i) + \beta (RT_{cpu}^{ref} - RT_{cpu}(i)) / RT_{cpu}^{ref}$$

(3)

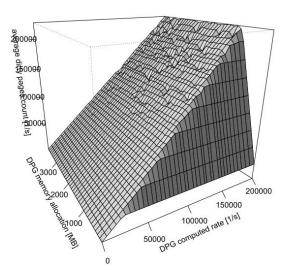

Figure 2. Mean response time vs. CPU utilization under

Where  $u_{cpu}^{ref}(i+1)$  is the desired CPU utilization,  $RT_{cpu}(i)$  is the measured response time, and  $RT_{cpu}^{ref}$  is the desired response time determined by SLO. The outer controller (RT controller) ensures that the value fed to the CPU controller is always within an acceptable CPU utilization interval  $[U_{min}; U_{max}]$ .

In our experiments, we set  $\beta$ =1.5. The CPU allocation is limited to the interval [10, 80], and the CPU utilization is also limited to the interval [10, 80]. The desired response time (RT) in all our experiments is 20 milliseconds.

Memory controller: In our experiments we noticed that increasing the number of Apache processes can increase the throughput. However, at some level, the performance is degraded drastically when the Apache processes consumed the whole available Memory. At that point, system starts swapping Memory contents into the hard-disk. This behavior adds more workload to the CPU, which is already overloaded by the big number of the processes. To keep the system away from bottlenecks, we implemented the Memory controller, designed in[2], to keep the CPU controller runs in an operating region away from the CPU contention:

$$a_{mem}(i+1) = a_{mem}(i) + K_2(i)(u_{mem}^{ref} - u_{mem}(i))$$

(4)

Where

$$K_2(i) = \lambda u_{mem}(i) / u_{mem}^{ref} \tag{5}$$

The controller aggressively allocates more Memory when the previously allocated Memory is close to saturation (i.e. more than 90%), and slowly decreases

Memory allocation in the low workload region. Along our experiments, we set  $u_{mem}^{ref}$ =90%,  $\lambda$ =1, and the limits of the controller are [64, 512], where the 64 is the minimum allowed Memory allocated size, and the 512 is the maximum allowed allocated Memory size.

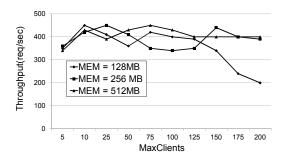

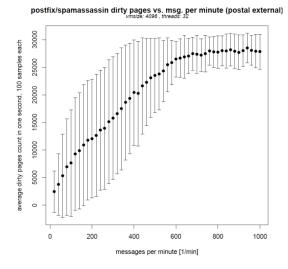

**Application controller:** after extensive experiments and monitoring of Apache behavior, we found that there was a specific value of *MaxClients* that gives the best throughput and the minimum response time as seen in figure 3.

Figure 3. Throughput vs. MaxClients under different hardware settings

Finding the optimum value of *MaxClients* was examined by former research e.g. [3]. Unfortunately, these optimization methods are not applicable to our case for many reasons: First, we have a dynamic resources. So, it will be difficult to dynamically determine the new optimum *MaxClients* value for each new resources allocation. Second, we dont have the chance to run an active optimization using our generated traffic, because this could influence the real service performance. Third, the optimum value is affected by traffic type and CPU utilization.

On the light of the mentioned problems, we designed our heuristic Apache controller to find the best Max-Clients value passively (i.e., depending on the real traffic). The Apache controller monitors four measured values to determine the best MaxClients: response time, throughput, CPU utilization, and number of running Apache processes. The controller saves the best record of these values. The best record is calculated by finding the record that satisfies the QoS response time metric and gives the highest throughput with less CPU utilization. With each new measurement of monitored values, Apache compares the current record with the best record, if it is better; the current record will be saved as the best record. While it is running, if the Apache noticed a violation of QoS metrics (response time in our case) it tries to predict the problem by the following rules:

**Rule1:** Apache processes starving problem: Apache processes starving problem occurs when Apache server runs big number of processes. As a result, CPU spends most of the time switching between these pro-

cesses while giving small slot of the time to each process. Such behavior causes requests to spend longer time in application queue, which end up with high response time and many timed-out requests. To eliminate this problem, the Apache controller reloads the Apache server with the last best record.

**Rule2:** Resources competition problem: The competition on resources is predicted by Apache controller as the following: response time increases, number of running apache processes reaches MaxClients value, and at the same time CPU utilization decreases (i.e. less than 90%).

As seen above, with both rules, the proposed Apache controller will not only look for the optimum Max-Clients value, but also will eliminate performance bottlenecks by keeping history of the last best running configurations.

#### 3. Experimental Setup in Future SOC Lab

Our experiment conducted on a testbed of two physical machines (Client and Server). Server machine (Future SOC Lab machine) is Fujitsu PRIMERGY RX300 S5 server with 4-cores, it is equipped with 12GB physical memory. Server runs Xen 3.3 with kernel 2.6.26-2xen-686 as hypervisor. On the hypervisor are hosted VMs with Linux Ubuntu 2.6.24-19. These VMs run Apache 2.0 as a web server in prefork mode. For workload generation, httperf tool [4] is installed on client machine. In the following experiments we deal with three VMs setup: First, Static VM, which is a virtual machine initialized with 512MB of RAM and limited to 50% of the CPU capacity. Second, Elastic VM with CPU/Memory controllers, it is a VM controlled with the CPU and Memory controllers seen in equations 1 to 5, the CPU limits of this machine is 80of CPU capacity, and the Memory is 512MB of RAM. Third, Elastic VM with Apache, it has the same setup of first VM except that it is equipped with our Apache controller in addition to CPU and Memory controllers. In all our experiments, SLO is to keep response time threshold (RT threshold) less than 20 milliseconds.

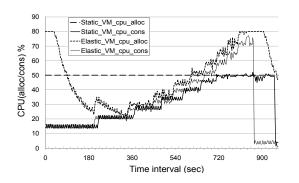

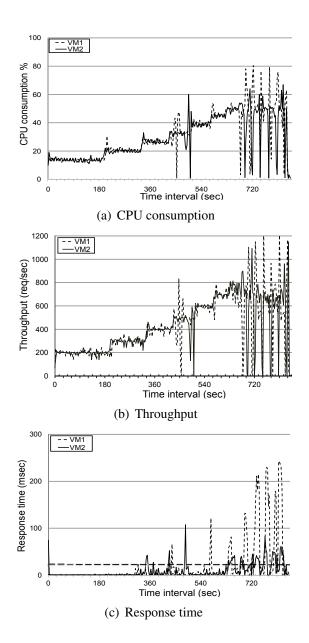

# 3.1. Static VM vs. Elastic VM response to step traffic

In this experiment, we would like to study our Elastic VM ability to cope with traffic change to maintain the specified SLO. As a basis for our experiments; we used dynamic web pages requests, in each request, the web server executes a public key encryption operation to consume a certain amount of CPU time. The step traffic initiated with the help of autobensh tool [4], it started with 20 sessions, each session contains 10 connections. The number of sessions increases by 10 with each load step. The total number of connections for each step is 5000, and the timeout for the request is 5 seconds. Throughput result from the generated web

traffic is seen in figure 4(b).

Each step of the graphs in figure 4(b) represents the throughput of a specific traffic rate. For instance, along the period 0 to 780 seconds; both VMs respond to requests successfully without any lost or time-out. On the other hand, after 780 seconds, the Static VMs CPU is saturated, which caused requests to wait longer in the TCP accept queue, and consequently increased response time. The long queuing results in a continues period of SLO violation as seen in figure 4(c).

Figure 4. Static VM vs. Elastic VM response to step traffic

The percentage of timed-out requests with the corresponding traffic rate is illustrated in table 1. The table started at 900 req/sec because there was no significant timed-out traffic before this rate. If compared to the Elastic VM for the same high traffic rate (i.e. 800 to 1200 req/sec), figures 4(a) to 4(c) show how the Elastic

| Requests rate(req/sec) | Static VM (timeout %) |

|------------------------|-----------------------|

| 900                    | 7.232                 |

| 1000                   | 15.328                |

| 1100                   | 18.258                |

| 1200                   | 27.772                |

Table 1. The timeout started after the Static VM received 900 req/sec.

VM was able to borrow more resources dynamically, serve more requests, maintain a low response time, and prevent SLO violation.

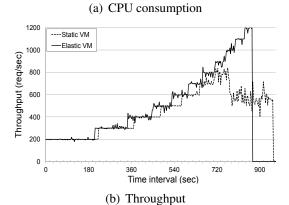

### **3.2.** Two Elastic VMs compete on resources

In the previous experiment, we studied the ideal case where the host was able to satisfy the Elastic VMs need for more resources to cope with the increase of incoming requests. In this experiment, we study the competition on the CPU between two Elastic VMs. To raise this competition, we pinned the virtual CPUs of two Elastic VMs into same physical core. To clarify the benefits of Apache controller usage, the step-traffic has been run two times simultaneously to both Elastic VMs, one time without Apache controller and another time with Apache controller.

The first part of the experiment is illustrated in figures 5(a) to 5(c). Figure 5(b) shows that Elastic VMs were not able to cope with the traffic rate higher than 800 reg/sec while the host committed only 50% of the CPU power for each VM starting from second #660, as seen in figure 5(a). The reason behind this fair sharing is Xen credit scheduler. During this experiment, we setup the scheduler with the same share for running VMs. According to competition on CPU, many requests are queued for a long time causing high response time and continues violation of SLO, as seen in figure 5(c). Moreover, many other requests are timedout before being served as seen in second and third columns of table 2. From the above experiments, we can conclude that Elastic VM can improve the performance if the host has more resource to redistribute, but in case of competition on resources, under the fair scheduling, Elastic VM (without) Apache controller merely behaves as a Static VM.

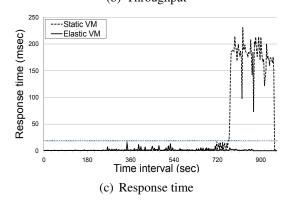

The previous experiment is repeated on two Elastic VMs (with) Apache controller. Figure 6(a) shows that in spite of the limited CPU capacity (50%) available to each VM, starting from second #660, apache controller does two improvements: First, the moment of the Apache reload is a good chance for the other Apache server to have more processing power and serve more requests. Second, after the reload, the Apache servers are tuned with a new MaxClients value, if this value achieved better performance, the Apache controller will keep it, otherwise it will con-

tinue looking for more optimum value. Third and fourth columns of table 2 show the improvement in terms of reductions of timed-out traffic and SLO violation.

Figure 5. Two Elastic VMs (without) Apache controller responding to step traffic

#### 4. Conclusions & Future work

In this part of the project, we have presented an implementation for elastic system architecture for optimizing resources consumption in consolidated environments. Our system includes three controllers CPU, Memory, and Application run in parallel to preserve SLO. We have evaluated our system in a real Xen based virtualized environment; the experiments show

Figure 6. Two Elastic VMs (with) Apache controller responding to step web traffic

|           | VM1                | VM2           | VM1      | VM2     |

|-----------|--------------------|---------------|----------|---------|

| (req/sec) | Timeout(without)   | Timeout(with) |          |         |

| 800       | 4.0%               | 0%            | 0%       | 0.2%    |

| 900       | 13.3%              | 23.8%         | 8.8%     | 8.2%    |

| 1000      | 20.5%              | 23.2%         | 16.52%   | 17.0%   |

| 1100      | 25.0%              | 35.0%         | 21.0%    | 22.0%   |

| 1200      | 31.0%              | 37.0%         | 26.2%    | 27.8%   |

|           | Violation(without) |               | Violatio | n(with) |

|           | 23.9%              | 26.4%         | 14.7%    | 16.8%   |

Table 2. Two Elastic VMs (without) Apache controller vs. two Elastic VMs (with) Apache controller responding to step traffic

that using Application controller maintains the performance and mitigates SLO violation and requests time-

out. Our immediate future work will include analyzing more applications such as database and their optimization feasibility in such dynamic resources allocation environment. The analysis will consider analytical models such as queuing analysis. We will also extend our work to be integrated with other resource management schemes like "running multiple instances" and "VM migration". Therefore, we will expand our experimental setup to more than one host in Future SOC Lab.

#### References

[1] P. Barham, B. Dragovic, K. Fraser, S. Hand, T. Harris, A. Ho, R. Neugebauer, I. Pratt, and A. Warfield. Xen and the art of virtualization. In SOSP '03 Proceedings of the nineteenth ACM symposium on Operating systems principles, pages 164–177, New York, NY, Oct. 2003. ACM Press.

- [2] J. Heo, X. Zhu, P. Padala, and Z. Wang. Memory Overbooking and Dynamic Control of Xen Virtual Machines in Consolidated Environments. In *Proceedings of IFIPIEEE Symposium on Integrated Management IM09 miniconference*, pages 630–637. IEEE, 2009.

- [3] X. Liu, L. Sha, Y. Diao, S. Froehlich, J. L. Hellerstein, and S. Parekh. Online Response Time Optimization of Apache Web Server. 2003.

- [4] J. T. J. Midgley. Autobench, 2008.

- [5] D. Mosberger and T. Jin. httperf A Tool for Measuring Web Server Performance. In *In First Workshop on Internet Server Performance*, pages 59–67, 1998.

- [6] VMWare. Vmware. http://www.vmware.com, 2010.

- [7] Z. Wang, X. Zhu, S. Singhal, and H. Packard. Utilization and slo-based control for dynamic sizing of resource partitions. 2005.

- [8] X. Zhu, Z. Wang, and S. Singhal. Utility-Driven Workload Management using Nested Control Design. American Control Conference, pages 6033–6038, 2006.

#### VMs Core-allocation scheduling Policy for Energy and Performance Management

Christoph Meinel, Ibrahim Takouna, and Wesam Dawoud

Hasso Plattner Institute (HPI)

University of Potsdam

Potsdam, Germany

{christoph.meinel, ibrahim.takouna, wesam.dawoud}@hpi.uni-potsdam.de

#### **Abstract**

In this phase of the project, we investigate the sensitivity of a VM performance running scientific multithreading applications to changes in clock frequency and VM performance dependency on Domain-0 for IO-intensive applications. Then, using sensitivity analysis to schedule VM to suitable core with suitable frequency settings. Currently, our work is built on a static heterogenous system, next we are going to investigate building a dynamic heterogenous system to realize power consumption proportional to a service requirements. However, our test environment showed that we can gain power savings up to 17%.

#### 1. Project Idea

Merging between multi-core processors and virtualization technologies has prompted us to investigate the possibility of achieving power saving for such combination for scientific multithreading applications. In this project, we investigated the advantages of virtualizing heterogeneous multicore systems where they could provide better performance per watt compared to homogeneous processors [1, 10, 7]. A single processor will contain hundreds of cores that vary in some micro-architecture features such as clock frequency, cache size, power consumption, and others [3], but these cores exploit the same instruction-set architecture. A single chip might have several complex cores and many simple cores. The simple cores are characterized as low-speed clock frequency, cache size, and low power consumption while fast cores are equipped with high-performance features such as high-speed clock frequency, cache size, and high power consumption. Consequently, their potential to achieve different levels of performance that meet applications heterogeneity has prompted researchers in the operating systems domain to implement heterogeneous aware schedulers [9, 8, 2].

With heterogeneity of applications characteristics, a Hypervisors scheduler is efficient if it assigns a virtual CPU (vCPU) to run on the appropriate cores based on the application characteristics in terms of CPUintensive, Memoryintensive, or IO-intensive. Further, it should have knowledge of the physical processors architecture and their characteristics such as cores clock frequency. By this knowledge, VMs with CPUintensive applications should be assigned to complex fast cores to be executed faster. Generally, scientific applications are CPU-intensive, multithreaded, and fewer CPU stalls due to infrequent memory accesses or I/O operations. On the other hand, I/O-intensive could be assigned to simple slow cores without losing significant performance and achieving the power savings. However, Hypervisors scheduling-policy is based on the round-robin algorithm to ensure fairness among VMs. Emerging heterogeneous system and virtualization bring more power savings and better resources utilization. This combination needs a new scheduler, which schedules each VM to an appropriate core based on its characteristics.

We used NAS Parallel Benchmarks [5] as CPUintensive application and netperf benchmark [6] as I/O-intensive application. We denoted performance sensitivity to CPU clock frequency as performancefrequency sensitivity and performance dependency on Domain-0 as performance- Domain-0 dependency. Our scheduling-policy based on these two categories: performance-frequency sensitivity and performance-Domain-0 dependency to assign a vCPU to the appropriate core. Consequently, the results showed good performance improvements for VMs with CPUintensive applications and for VMs with IO-intensive applications as well. Finally, our heterogeneous experimental environment achieves promising power savings reach to 17% which theoretically could reach to 45% . The power savings are gained from this architecture, which runs on two cores with high frequency and other two cores with low frequency.

#### 2. Used Future SOC Lab Resources

The evaluation tests were performed on Fujitsu PRIMERGY RX300 S5 server. It has a processor of Intel(R) Xeon(R) CPU E5540 with 4-cores and the frequency range is 2.53GHz to 1.59GHz. the server is equipped with 12GB physical memory. Additionally, We used ServerView Remote Management to monitor power consumption for CPU.

#### 3. Findinds: VMs Sensitivity Analysis

In this section, we analyzed sensitivity of VMs performance to changes in CPU clock frequency for VMs that run CPU-intensive and IO-intensive applications. Then, we illustrated dependency of VMs on Domian-0 for VMs with IO-intensive applications.

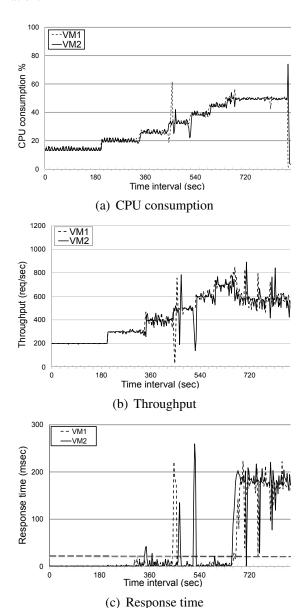

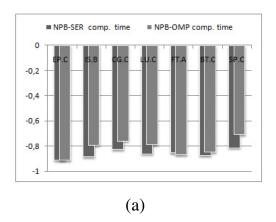

## 3.1. VMs with NBP Sensitivity Analysis

To analyze VMs performance-frequency sensitivity, we used NBP-SER and NPB-OMP benchmarks as CPUintensive programs. In this experiment, we pinned vCPUs of Domain-0 to cores (0,1) and vCPUs of VMs were pinned to the another two cores (2,3) to avoid Domain-0s influence on the VMs; in other words, to prevent Domain-0 from being queued with the VMs in the same queue. First, the experiment was run while the cores (2,3) were set to run with high frequency  $F_F$  =2.53GHz as fast cores. Then, it was run again after changing frequency settings of the cores (2,3) to low frequency  $F_S$ =1.59GHz as slow cores. Finally, we used the price elasticity of demand economics formula to determine programs completion time and throughput sensitivity of clock frequency. We considered T the completion time and Th the throughput as the demand, and F clock frequency as the price.  $E_{T,F}$  is the completion time sensitivity of clock frequency, and  $E_{Th,F}$  is throughput sensitivity of clock frequency.

$$E_{T,F} = \frac{T_F - T_S}{F_F - F_S} * \frac{F_F + F_S}{T_F + T_S}$$

(1)

$$E_{Th,F} = \frac{Th_F - Th_S}{F_F - F_S} * \frac{F_F + F_S}{Th_F + Th_S}$$

(2)

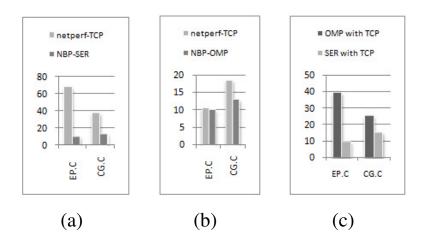

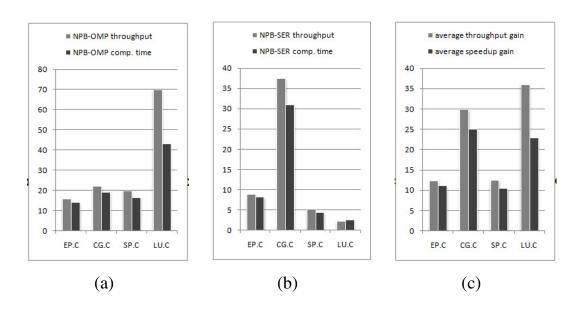

Due to the inverse relationship between CPU frequency and completion time,  $E_{T,F}$  values are negative, so completion time increases as CPU frequency decreases and vice versa. On the other hand,  $E_{Th,F}$  values are positive because of the direct relationship between CPU frequency and throughput. Program speedup depends on program characteristics, so it does not have a liner relationship with CPU frequency. However, CPU-intensive programs might have a semi-liner relation with frequency because of either infrequent memory accesses or I/O operations. Figure

1 shows NPB-OMP and NPB-SER benchmarks performancefrequency sensitivity (i.e., completion time and throughput). NPB benchmark each program has different memory access behavior and various interprocess communication patterns. These characteristics determine sensitivity of a program to frequency changes. For example, the completion time of EPOMP and EP-SER programs had the same sensitivity and they gained the highest sensitivity. The similarity between these two programs is that EP-OMP a multithreaded program but has negligible inter-process communication and EP-SER is a single thread program without inter-process communication. Further, EP-OMP is seldom memory access compared with CG-OMP and LU-OMP. Generally, NPB-SER programs sensitivity to frequency changes was higher than NBP-OMP due to the sequential execution of instructions in NPB-SER and inter-process communication patterns or IO operations in some of NBP-OMP programs such as CG and BT respectively. On the other hand, NBPOMP programs with intensive inter-process communication were less sensitive to frequency such as CG-OMP and LUOMP. FT, a mixed type program, almost had the same sensitivity in NPB-SER and NPB-OMP. Unlike LU-OMP, BT-OMP includes a number of I/O operations that do not need synchronization among its threads.

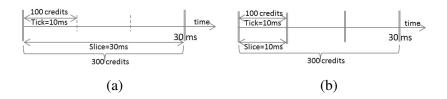

#### 3.2. VMs with I/O Sensitivity Analysis

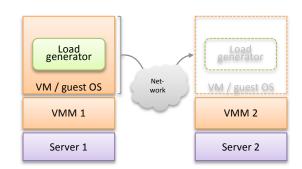

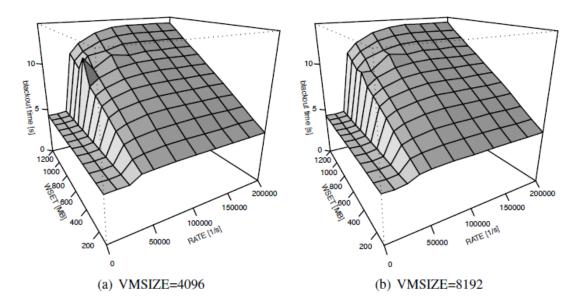

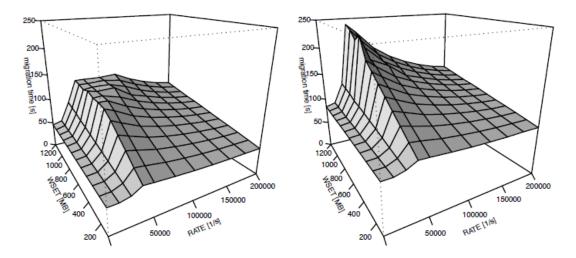

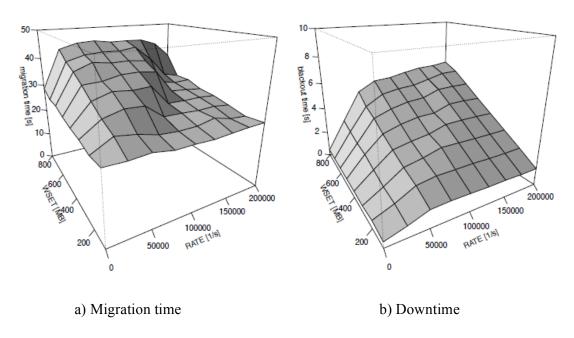

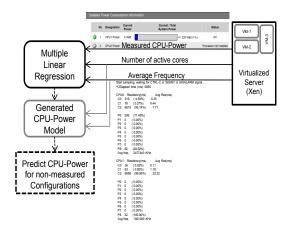

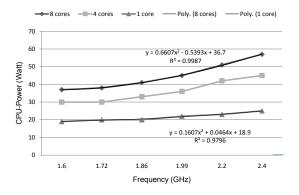

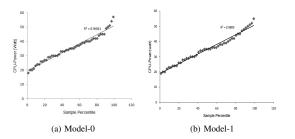

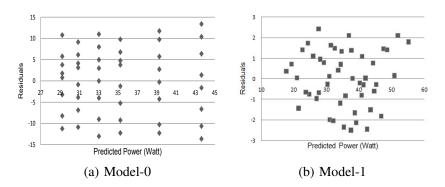

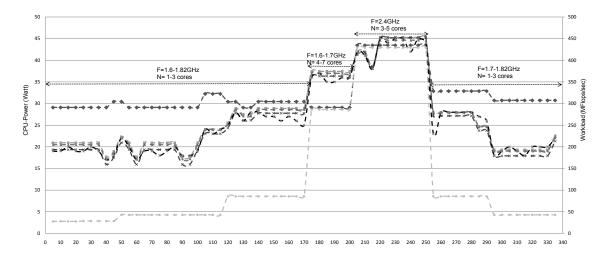

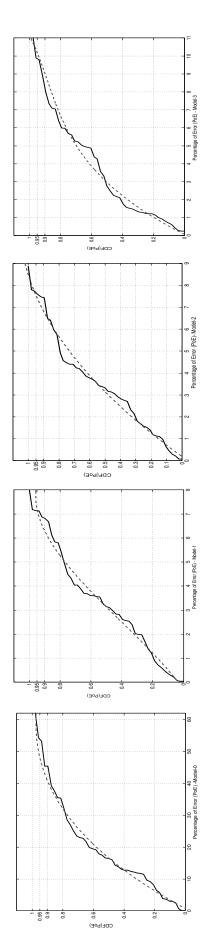

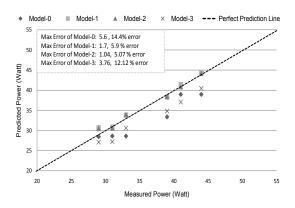

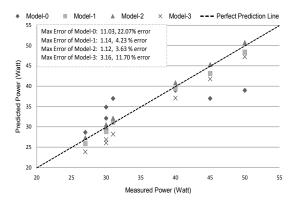

We analyzed sensitivity of VMs performance with I/Ointensive to CPU frequency. Then, as I/O operations depend on Domain-0, we tested VMs performance-Domain-0 dependency.